Dinamikus prioritás boost

Az ütemező hoz döntéseket a jelenlegi prioritása egy szál, amely lehet az alapvonal fölé. Vannak olyan helyzetek, ahol van értelme emelni a prioritást egy szál.

Például befejezése után az input-output műveletek nagyobb prioritást az áramlás, amely lehetővé teszi, hogy gyorsan kezdődik, és lehet újra megindítja az IO műveletet. Ezáltal a rendszer ösztönzi az interaktív patakok és támogatja a foglalkoztatást, az input-output eszközök. Az összeg, amellyel a kiemelt megnő, nem dokumentált, és attól függ, hogy az eszköz (ajánlott értékeket lemez, CD - 1, hálózati - 2, a billentyűzet és az egér - a 6. és a hangkártya - 8). Később során több alkalommal szelet prioritás fokozatosan csökken az alapvonalra.

Más példák ilyen helyzetek közé tartoznak: patak ébredés után szemafor várakozási állapot egy esemény; folyamának befogadására való hozzáférés az ablak bemenet.

Dinamikus prioritás boost is megoldja a problémát az éhezés folyik sokáig nem kapnak hozzáférést a processzor. Megtalálása ilyen áramlások, üresjáratban körülbelül 4 másodpercig. A rendszer átmenetileg növeli a prioritást 15 és ad nekik két alkalommal szeletet. A mellékhatása ez a technológia lehet a megoldás az ismert probléma az elsőbbségi inverzió [Tanenbaum]. Ez a probléma akkor jelentkezik, ha az alacsonyabb prioritású szál tart erőforrás blokkoló kiemelt hullámok alkalmazásával az erőforrás. A megoldás az, hogy mesterségesen növeljék a prioritás egy ideig.

Dinamikus növekedést célzó prioritások optimalizálása a teljes rendszer kapacitását, azonban az ebből származó előnyöket, nem minden alkalmazás. Letiltása dinamikusan növekvő prioritást is elvégezhető SetProcessPriorityBoost SetThreadPriorityBoost és funkciókat.

Az érték az idő szelet

Idő szelet mérete kritikus a hatékony működéséhez az egész rendszer. interaktív rendszerek minőségi fenn kell tartani, és ugyanabban az időben, hogy ne túl gyakori váltás környezetben. Valószínűleg egy optimális értéke kvantum (a második) kell biztosítani a szolgáltatást anélkül, hogy a felhasználó váltás kérés processzor, amely rövid időt, ami után általában generál kérelem bemeneti és kimeneti. Ebben az esetben, az ütemezési költségek minimálisak, és elfogadható reakcióidőt.

Válasszon a rövid és hosszú értékeket lehet tenni a panel „Tulajdonságok” a „Sajátgép”. Az érték a kvantum paraméter beállított HKLM \ SYSTEM \ CurrentControlSet \ Control \ PriorityControl \ Win32PrioritySeparation adatbázis.

- Mi a relatív prioritását az áramlás?

A második komponens a teljes áramlás a prioritás relatív prioritása külön áramban. Hangsúlyozni kell, hogy a prioritási osztálytól kapcsolatos eljárást, valamint a relatív prioritás - külön folyamok a folyamatot. Flow lehetséges átlaga az egyik a hét lehetséges relatív prioritások: Idle (elvárás), a legalacsonyabb (alsó), normális alá (a normális alá), Normal (normál), a normális fölé (a normálisnál magasabb), a legmagasabb (magasabb) vagy Time Critical (kritikus idő).

5.2 táblázat. A relatív prioritása adatfolyam

- Mi az a „dinamikus prioritás” flow?

Sok operációs rendszer biztosítja a képességét, hogy módosítsa prioritások áramlását az élet. Prioritás változás mehet végbe kezdeményezésére a patak kifejezés azt jelenti, hogy a megfelelő hívást az operációs rendszer, vagy a felhasználó által kezdeményezett, amikor elvégzi a megfelelő parancsot. Ezen túlmenően, az operációs rendszer maga is változtatni menet prioritásokat, a helyzettől függően uralkodó a rendszerben. Az utóbbi esetben az úgynevezett dinamikus, szemben a megváltoztathatatlan, állandó, prioritásokat.

- A koncepció a cache és cache.

A cache memória egy nagy sebességű memóriát, helyezzük egy chip a CPU, vagy a külső a CPU. A cache egy nagy sebességű puffer között a CPU és a viszonylag lassú fő memória. Az ötlet a cache alapuló becslés a legvalószínűbb a CPU eléri a memóriába. Az alapja ennek a megközelítésnek az az elv, a térbeli és időbeli településen a program.

Ha a CPU alkalmazható bármely tárgy RAM, nagy valószínűséggel a CPU hamarosan újra bekapcsolja az objektumot. Egy példa erre a helyzetre lehet kód vagy adat ciklusokban. Ez a fogalom leírása elvének időbeli településen, amely szerint a gyakran használt memória objektumokat kell „közelebb” a CPU-t (a cache).

Hogy megfeleljen a tartalmát a cache memória és RAM-használat három módszer a bejegyzést:

· Írja keresztül (írj keresztül) - ugyanakkor a memória frissül a cache memória.

· Pufferelésű pass-through rekordot (pufferelt írási keresztül) - információ megmarad a cache puffer előtt írt a memóriába, és felülírja a memóriában azokban ciklusban, amikor a CPU nem foglalkozni a problémával.

· Visszaírási (write back) - változó használt bitek a címkemezőbe, és a vonal átírása a memóriában csak akkor, ha a bit 1 változásokat.

Általános szabály, hogy minden rögzítési módszerek eltérő keresztül, hogy nagyobb teljesítményre és elhalasztja a csoport ír a memóriába.

A szerkezet a cache memória kétféle adat blokkok:

· Kijelző adatmemória (valós adatok, sokszorosított emlékezetből);

· Tag memória (jelzéseket a helyét a tárolt adatok a memóriában).

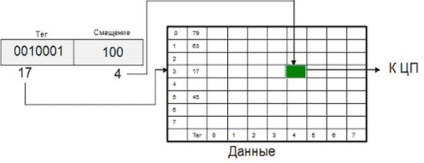

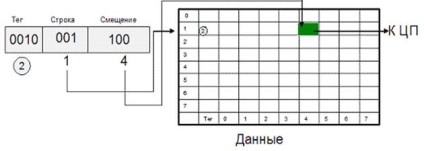

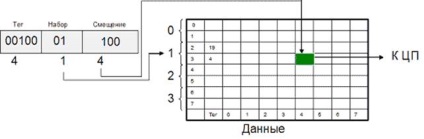

Megjelenítése adatmemória hely a gyorsítótár sort osztjuk - blokkok fix hosszúságú (például 32, 64 vagy 128 bájt). Minden gyorsítótár sor tartalmazhat folytonos bájtos igazított blokk memória. Melyik blokk memória leképezve egy adott gyorsítótár sor, a címkét úgy határozzák meg, és a kijelző algoritmus. Feltérképezésével algoritmusok RAM cache Háromféle cache memória:

teljesen asszociatív cache;

cache közvetlen leképezés;

Több asszociatív cache.

Az egyik fő előnye ennek a módszernek kijelző - jól hasznosítják a RAM, mivel Nincsenek korlátozások, hogy milyen egység is megjelenik egy bizonyos gyorsítótár sor. A hátrányok közé tartozik komplex hardver végrehajtását ez a módszer nagy mennyiségű áramkört (főleg komparátorok), ami növeli a hozzáférési idő egy ilyen cache, és növeli a költségeket.

14. ábra. A rendszer a szervezet a cache memória az MP Motorola MC68020

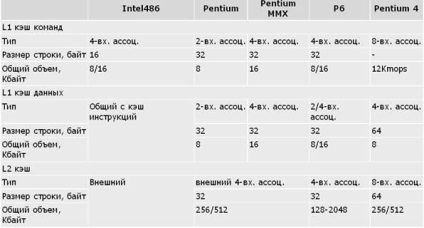

Ez leképezőalgoritmusra előnyeit egyesíti mind a teljesen asszociatív cache (jó memória kihasználása, nagy sebességű), és a közvetlen gyorsítótár-hozzáférés (az egyszerűség és az olcsóság) csak egy kicsivel rosszabb, hogy ezek a jellemzők az eredeti algoritmus. Ez az oka annak többszöröse asszociatív cache a legelterjedtebb (táblázat. Jellemzői cache memória a CPU alrendszer IA-32).

Táblázat. Részletek az cache memória alrendszer IA-32 CPU

Megjegyzés: Az Intel-486 használ egy utasítás cache és egy adat szint. A Pentium Pro L1 adat cache - 8KB 2-bemenet asszociatív, más modellekben P6 - 16K 4 bemeneti asszociatív. A Pentium 4 felhasználása mikro-L1 cache (cache útvonalat) helyett L1 utasítás cache.

Használhatja a Princeton architektúra a szervezet cache memória (vegyes cache utasítások és adatok, például az Intel-486). Nyilvánvaló (és elkerülhetetlen a Neumann rendszerek külső a CPU cache) megoldás nem mindig a leghatékonyabb. A szétválás a cache, az utasítás cache és az adatok cache (gyorsítótár Harvard architektúra) javíthatja cache teljesítményét az alábbi okok miatt:

Sok modern processzorok a futószalag építészet, amelyben a szállító egységet párhuzamosan működik. Így az utasítás lehívás és az adatokhoz való hozzáférést a parancs végezzük különböző szakaszaiban a csővezeték és használata külön cache lehetővé teszi, hogy ezeket a műveleteket elvégezni párhuzamosan.

· Utasítás cache lehet megvalósítani csak olvasható, ezért nem szükséges a végrehajtás bármely write-back algoritmusok, így ez a cache egyszerűbb, olcsóbb és gyorsabb.

Éppen ezért a legújabb modell az IA-32, mivel a Pentium, a szervezet az első szintű cache segítségével a Harvard architektúra.

Cache teljesítmény kritériumok lehet tekinteni, hogy csökkentsék az átlagos hozzáférési idő memória összehasonlítva a rendszer gyorsítótár nélkül. Ebben az esetben, meg tudjuk becsülni az átlagos elérési idő a következő:

15. Tav = (Thit x Rhit) + (Tmiss x (1 Rhit))

ahol Thit - hozzáférési idő a cache memória érintkezés esetén (beleértve time-to-azonosítására miss vagy a hit), Tmiss - a szükséges időt rakat a fő memóriából a gyorsítótár sor abban az esetben, a cache és az azt követő szállítás a kért adatokat a processzor, Rhit - az alkalmazás gyakorisága találatot.

Nyilvánvaló, hogy minél közelebb Rhit értéke 1, akkor a közelebbi értéket Tav a Thit. hit gyakorisága döntően az építészet, a gyorsítótárat és a hangerőt. Hatása a jelenlétében és távollétében a cache és térfogatát növelni processzor teljesítménye táblázatban mutatjuk be. A méret és a hatékonyság a cache memória

Táblázat. A méret és a hatékonyság a cache memória

Az összetett ez a mechanizmus jelentősen befolyásolja

elhelyezési stratégiát, amely meghatározza, milyen helyen cache

helyezni az egyes blokk fő memória.

Attól függően, hogy a módszer elhelyezése a fő memória adatokat a cache memória van háromféle cache memória:

· Közvetlen leképezett cache (lokalizálják);

· Teljesen asszociatív cache;

· Több asszociatív cache vagy részben asszociatív.

Set-asszociatív típusú, vagy részben asszociatív típusú kijelző - az egyik lehetséges kompromisszum, amely egyesíti előnyeit az asszociatív és közvetlen módszerek. Cache (és címkék és adat) fel van osztva több modulból. A kapcsolat a modul és az OP-egységek olyan kemény, mint a közvetlen leképezés. De hol van a modul sorok tetszőleges blokkok és keresni a húr a modul az asszociatív elv. Ez a módszer a megjelenítésére a legelterjedtebb modern mikroprocesszorok.

- Mi határozza meg a hatékonyságát a cache.

- Miért kell TLB (fordítást elkerülő puffer).

legújabb. TLB egyszerűsített rendszer ábrán látható. 5. Az asszociatív puffer adás.

Ahhoz, hogy megtalálja oldalak, amelyek nem a TLB, a virtuális memória menedzser használ laptáblák által létrehozott szoftver. Elméletileg, a laptáblázat ábrán látható. 3. Fogalmi laptáblázat rendszer.