A kölcsönhatás a memória és a CPU

Query feldolgozó processzor nyugszik egy sor rendszer logikája (más néven a lapkakészlet), többek között tartalmaz egy memória vezérlő. A memória vezérlő teljesen „átlátszó” a programmista͵ de ismerik annak építészeti jellemzőit nagyban megkönnyíti optimalizálás-CIÓ memória megosztását.

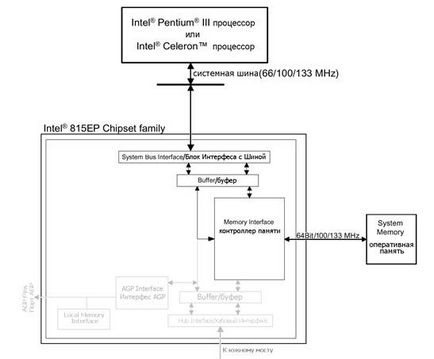

Készülék Northbridge chipset Intel 815EP tartalmazó (többek között) a memória vezérlő

A busz vezérlő (BIU - Bus Interface Init), „beültetett” a Northbridge chipseta͵ a kérelem kézhezvételét a processzor helyzet alapján, vagy elküldi a megfelelő szert (a mi esetünkben - pas RAM memória vezérlő), vagy hozza a kérelmet a sorban, ha az ügynök jelenleg elfoglalt valamit. Szükség van egy sorban annak a ténynek köszönhető, hogy a processzor küldheti a következő kérés nélkül várja a gyártás befejezése az előzőt, és ha igen, a kérdést kell tárolni valahol.

Mivel a függőség a memória vezérlő otarhitektury működik a memória, vagy csak a rendszerbusz sebessége (szinkron szabályozó) vagy al-memória Heréd más frekvencia (aszinkron vezérlő). A szinkron vezérlők korlátozzák felhasználó ?? s PC a választás a memóriát, de másrészt, az aszinkron vezérlők kisebb termelékenységet-ing. Miért? Elsősorban miatt frekvencia eltérés, olvasni az adatokat nem közvetlenül továbbítja a busz vezérlő, és a Com-ditsya első hajtás a köztes puffer, ahol a busz vezérlő képes lesz letölteni őket vele a kívánt sebességet. (Hasonló situa-CIÓ figyelhető meg a bejegyzést.) Másodszor, ha a frekvencia a rendszerbusz és a memória órajel mint nem egész számok, mielőtt a csere meg kell várnia a jelenlegi befejezéséig órajel impulzus. Ezek a késedelmek fordulnak elő a két (köznyelvben büntetés):

el, amikor az olvasási adatoknak a busz vezérlő.

Mindez nagyban növeli a várakozási idő a memória alrendszer - .. Re pro-mezhutka idő óta a kérelem elküldését adatokat lekérdezni. Τᴀᴋᴎᴍ ᴏϬᴩᴀᴈᴏᴍ aszinkron vezérlő működő SDRAM PC-133 busz rendszer memória ?? e 100 MHz, elveszti szinkron kolléga, fut ugyanazon a gumiabroncs ?? e az SDRAM PC-100 memória.

Bus vezérlő, a memória vezérlő a bejelentés kézhezvételét, hogy a kért adatok készen, várva a kibocsátás a gumiabroncs és továbbítja azokat a processzor szakaszos üzemmódban. Mivel a függőség ottipa busz órajelenként lehet vezetni egy és négy darab adatokat. Tehát, a pro-tsessorah KB, P-l és P-III tett egy átviteli ciklusonként, az Athlon processzor - két, a P processzor-4 - négy.

Ettől a pillanattól kezdve az adatok jön be a cache és hozzáférhetővé kell tenni a processzort.

Controller buszrendszer feldolgozásáért felelős lekérdezések és kényszerült-schenie adatok között a processzor és a chipset, az alábbi funkcionális komponensek: egy adatátvitel (Processor Forrás Szinkron Óra adó), kéri ütemező (Command Queue - CQ), vezérlők-ra kérelem várakozási (Kontroll A rendszer Queue - CSQ) hatóanyag és tranzakció - XCA). A fennmaradó komponensek shi HN vezérlő jelen ábrán. 2.11 van szükség, hogy támogassa a szonda, bund, hogy a téma megvitatás alatt nem alkalmazható, ezért nem mérlegelik-versenyeken.

Adatátvitel - egy bizonyos értelemben, annál nagyobb a „csupasz” busz vezérlő megérti a busz protokoll, és az a nap ?? e gondoskodás a kommunikáció a processzor. Felkérést kapott a processzor ne-Reda lekérdezés tervező, ahonnan elküldik a megfelelő vezető szereket, azok megjelent.

A válaszokat szerek tárolására három különálló sorok: olvasni sorban (SysDC Read Sor - SRQ), a memória írási queue (Memory Write Sor - MWQ) és a PCI busz sorban bejegyzéseket (PCI / A-PCI Write Queue - AWQ). Megjegyzés: ebben az esetben beszélünk olvasás / írás a processzor, hanem a forgalom! Τᴀᴋᴎᴍ ᴏϬᴩᴀᴈᴏᴍ, memória tárolja a rekordokat az összes adatot továbbított-MYE a memóriából a processzor, de a processzor nem rögzítik a memória!