A felület JTAG

JTAG (ejtsd: „Jay-tag” ;. angol rövidítése vegyes Test Action Group) - a neve a munkacsoport fejlesztése az IEEE 1149. Később ez a csökkenés szilárdan velük kapcsolatban kifejlesztett speciális hardver-alapú felületet az IEEE 1149,1 szabvány. A hivatalos neve a Standard Test Access Port és Boundary-Scan Architecture. A felületet úgy tervezték, hogy csatlakoztassa a komplex digitális chip vagy nyomtatott áramköri szintű eszközökhöz a szabványos berendezések tesztelése és a hibakeresés.

A mai napig a felület vált az ipari szabvány. Szinte minden, mint egy komplex digitális chip képezi ezt a felületet:

· Output vezérlő gyártásához IC;

· Tesztelés gyűjtött nyomtatott áramköri lapok;

· Firmware chip memória;

· Hibakeresés munkát a tervezés hardver és szoftver.

vizsgálati módszert végrehajtani a standard nevezték Boundary Scan (határ scan). Név tükrözi az eredeti ötlet a folyamat: a chip osztják funkcionális blokkok, amelyek bemeneteket lehet húzni a többi áramkör, szállít egy előre meghatározott jelfeldolgozó egység megbecsülni a kimenetek állapota. Az egész folyamat végeztük kizárólag speciális csapatok JTAG interfész, nincs fizikai beavatkozás szükséges. Azt is kidolgozott egy szabvány, amely folyamatirányító nyelv - Boundary Scan Description Language (BSDL).

A szabvány lehetővé teszi, hogy csatlakoztassa a nagyszámú eszközt (chip) egy fizikai port (csatlakozó).

Port teszt (TAP - Test Access Port) egy négy vagy öt dedikált csap: TCK, TMS, TDI, TDO, és (adott esetben) TRST.

JTAG-port áramkör és Boundary Scan sejteket.

Funkcionalitás ezeket a sorokat:

TDI (teszt adatbevitel - «teszt adatbevitel") - a soros adat input határ scan. Parancsok és adatok bekerülnek egy chip, amely kiadási felfutó éle TCK jel;

TDO (vizsgálati adatok kimenet - «vizsgálati adatok output") - a kimenet soros adatokat. Parancsokat és adatokat a chip kimenetét a kimeneti lefutó éle TCK jel;

TCK (teszt óra - «teszt clock") - működését órák beépített periféria letapogató ellenőrző automata. A maximális pásztázási sebesség perifériás cella függ a hardver és jelenleg csak a 25 ... 40 MHz [forrás nem meghatározott 354 napos];

TMS (teszt üzemmód kiválasztásához - «kiválasztási teszt üzemmód") - egy átmeneti rendszer / teszt üzemmód kapcsolóval és a különböző vizsgálati üzemmódok.

A munka azt jelenti, hogy biztosítsák a JTAG jelek ellenőrzése alá tartozik gép, beépített chip. gép államok definiált jelek TDI és TMS mérõnyílást. Egy bizonyos kombinációja TMS és TCK jeleket ad parancsot a parancssorba az a gép, és annak végrehajtását.

A vezérlő áramkör JTAG interfész.

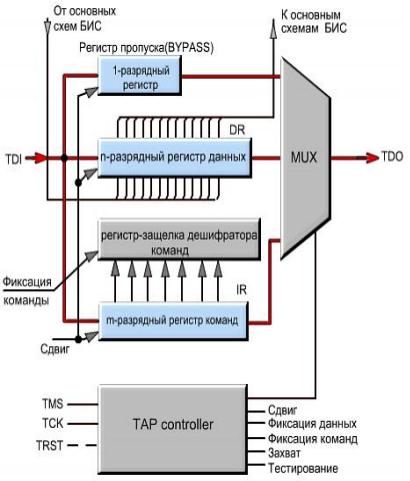

A szerkezet a program a következők:

- Három léptető regiszterek (utasítás regiszter (IR), hagyja regiszter (kézi) és adat regiszter (DR);

- A multiplexer kimenete (MUX);

- A vezérlő (TAP Controller).

Ábra. 13.1. JTAG interfész hardver.

A fő regiszter adatregiszterhez, ez szolgál az adatforrás és a vevő, ha a JTAG láncok bármely parancsokat. Szemszögéből a vezérlőberendezés, az adatregiszter egyike a három léptetőregiszterek tartalmazza kivezetése közötti ellátására bemeneti információt (műsorszám TDI) és egy kimeneti kapcsa információk fogadására (terminál TDO).

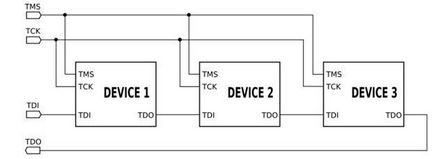

Ha a testület több eszköz támogatja JTAG, azokat kombinálhatjuk egy közös lánc. Egy egyedülálló jellemzője az a képesség, hogy JTAG programozás nem csak a mikrokontroller (vagy FPGA), de kötve következtetéseiben flash memória chipek. Sőt, két módja van a flash memória programozás JTAG: rakodó keresztül egy későbbi adatcsere révén a processzor memóriájában, vagy a közvetlen irányítást chip terminálok.

Ábra. 13.2. csatlakozni több eszköz egyetlen felületen.

A szoftver együttműködik ezen a felületen végre JTAG Élő termékeket. JTAG élő család szoftver termékek elsősorban a fejlesztők számára, akik hibakeresés új vagy meglévő termékek. JTAG élő alapul határ-scan - ez a módszer pontosan beméri hibák digitális áramkörök. Ugyanakkor termékek JTAG élő nem hivatásos automatizált rendszerek; az összes vizsgálatot manuálisan létrehozott. Ezért nem kell a net-lista a munkát. Egyszerűen válassza ki a szükséges következtetéseket chipek JTAG támogatás és húzza őket a munkaterületre. Akkor ellenőrizze a kapcsolatot a megadott pontokat, rövidzárlat, vagy úgy egy logikai érték, hogy egy adott láncban. Így lehetőség van arra, hogy a munka még összeszerelés táblák!

JTAG Élő lehetővé teszi, hogy több verzió a vizsgálat modul csatlakozik a számítógéphez. Ezek az eszközök működnek szabványos USB-PG által Altera és Xilinx. Arra is lehetőség van, hogy csatlakoztassa a JT3705 / USB vezérlő JTAG Technologies. Meg lehet kezdeni most ingyen. Töltse az alapváltozat JTAG élő és biztonságban maradjon. A Buzz, akkor gyorsan azonosítani akár két csatorna határ-scan és azonnal integritásának ellenőrzésére a lánc. Az ellenőrzés után az infrastruktúra, Buzz azonnal lehetővé teszi, hogy dolgozni alkatrészláb.

Buzz is rendelkezik egy nagyon kényelmes módja annak, hogy ellenőrizze a kapcsolatot a két csap, ha csatlakoznak a vizsgált áramkör. A program termel az ismerős hangot, hogy a modellek jelzik a szokásos multiméter. A mérési ablakban kiválaszthatjuk a kimenete az IC, amelyek meghatározzák a kívánt logikai szint, és mérlegeli az egyéb kiadási ugyanazon vagy egy másik kristály.

Próbáld megtekintéséhez felvonó ellenállás beállítása a megfelelő kimeneti meghajtó egy harmadik államban (High-Z). Buzz azt is lehetővé teszi, hogy a leolvasás egy csoportja áramkörök, amennyiben kapcsolódnak egymáshoz, azaz túl a képességeit a hagyományos multiméterrel. Bármilyen érték beállítható a kiválasztott lábát chip és ellenőrizze a jelet a többi beviteli eszközök a táblán.

Ha azt szeretnénk, hogy tovább egyszerű „folytonosság”, és tapintás egyes láncok, akkor fontolják meg programokat létrehozni teszt JTAG Élő Clip és Script. C keresztül tesztprogramok tárolható ipari célra. Clip - ezt a kiegészítőt, amely lehetővé teszi, hogy manuálisan létrehozni a szükséges vizsgálatokat annak meghatározására vektor lánc. Script egyesíti a jó határ-scan és funkcionális teszt segítségével a beépített programozási nyelv PythonTM. Azonban vegye figyelembe. hogy élő Clip és Script platnae programot.

Hardver felület támogatás - JT 3705 / USB.

Ábra. 13.3. Külső A JT 3705 / USB Explorer vezérlőt.

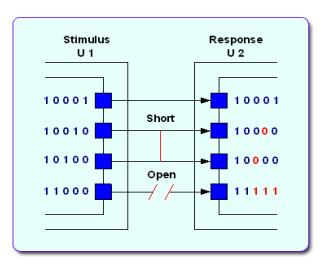

Külső tesztvegyületeket (Chip külső kapcsolat teszt) segítségével JTAG

• Tegyük fel, hogy a rendszer a két hibát:

• zárása között 2-es és 3 és

• Tegyük fel, hogy az áramkör látható, mint a vezetékes-és szakadás, mint a

állandó jelenléte egy logikai 1.

Ris.13.4. A vizsgált vegyületeket.

Áttekintés opensource JTAG eszközökkel.

ldoolitt / jtag.html) első kísérlet fejlődő szoftveres réteg eléréséhez a fogadó (host oldali hozzáférés) a JTAG Test Access Portok. A legtöbb fejlesztő a fejlődő azok egymást átfedő megoldások szingularitásokat amikor megpróbálja elérni a hordozhatóság között JTAG adapterek végre hibakeresőkkel, illetve annak végrehajtása Autokeresés eszközök a JTAG láncban. Próbálja kialakítani egy egységes közösség Components ezen feladatok alapján közös API a középszintű hozzáférést a JTAG eszközök. Ez lehetővé teszi a fejlesztők a magas szintű alkalmazások nem újra feltalálni a kereket, ha dolgozik, alacsony szintű detalyamt mint a JTAG csapok, stb